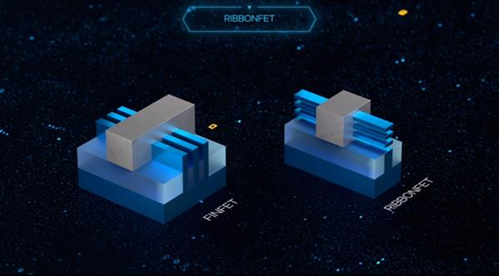

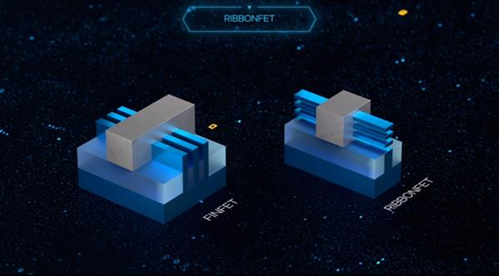

本文将帮助您了解高级英特尔技术流程和高级系统水平技术的全部细节...由本文引用:1。英特尔18A流媒体流媒体流式传输过程的技术过程将于2025年上半年完成。在2025年底启动。在2025年底启动,并将在2026年的上半年发布2026年的Inter forter for 2025 Intel forter Intel intel intel intel intel intel intel intel intel intel intel forter intel intel intel forty forty forter intel intel inter 3 efters forty forter intel int forty forter的范围的3季度与Intel 3的增长相比。预计芯片密度将增长15%,增加30%。 【英特尔18a |查看我们最大的变化过程】Intel 18a采用了两个主要的技术突破:彩色链接式晶体管技术和电源Backvia电源技术。 【英特尔18a |查看我们的MostribbonFet更改libbonFet完全浸没的栅极晶体管的过程:在芯片工艺技术的连续演变过程中,作为CHIP密度不断增加,泄漏问题引起的现象的变暖似乎是一种“诅咒”,并且已成为前路的主要障碍之一。色带是解决这一挑战的有效解决方案。通过十多年来,英特尔(Intel)是英特尔(Intel)最重要的晶体管技术之一,英特尔(Intel)实施了完全广泛的栅极体系结构(GAA),并具有垂直堆叠的色带通道,提高了晶体管的密度和能量效率,从而实现了准确的当前控制,并减少了进一步的问题,以实现进一步的跨跨晶体管收缩问题。此外,功能区FET在静电性能时改善了每个瓦的性能,最小电压(VMIN)操作。无论电压是什么,它都可以提供更强的电流驾驶,从而使晶体管开关更快,从而进一步改善了晶体管性能。色带还通过不同的带和多种类型的阈值(VT)电压提供了高度的可调性CH为芯片设计带来了更大的灵活性。 L Powervia背部电源:随着越来越多的使用情况需要较小,更高的密度和更强的性能晶体管才能满足计算强度不断增长的需求,而混合信号线和电源总是在晶圆中“抓住”相同的空间,从而导致晶体管紧密和增加晶体管。电力侧供应技术Powervia出现通过将粗金属层和颠簸在芯片后面移动,并将纳米尺度通过硅孔(Nano-TSV)嵌入到每个通用电池中,以提高电源的效率。这项技术在ISO4%功耗方面取得了最大的提高,大大降低了自然电阻(IR)以降低和提高单位使用5%至10%。 2024年2月,英特尔扩大了其路线图:[Process Node,Team Pele of] L Intel 14A使用高EUV技术,并有望在2027年之前实现大规模的大规模劳动。LIntel还计划推出更改的节点AL的版本ONG以满足客户不同需求的方式。其中,P版本至少获得了5%的性能提高(Intel 18A-P); E的折叠已扩大其功能,例如RF和电压调节(Intel 16-E,Intel 3-E,Intel 14a-E);通过使用Silicon(Intel 3-T,Intel 3-PT)使用孔,为3D堆叠进行了优化的T版本。 2。包装技术高级包装高级包装技术的重要性可以将单个设备上的各种功能,流程,大小和制造商的芯片结合在一起,并以灵活,有效的能源和经济成本的方式创建基于系统的(SOC)芯片。因此,更多的AI芯片制造商更喜欢这项技术。 [英特尔高级包装:有助于大型AI芯片集成的技术力量]英特尔英特尔的高级包装解决方案以及先进的系统包装和测试(Intel Foundry ASAT),包括FCBGA 2D,FCBGA 2D+,2.5D,2.5D,EMIB 3.5D,FOVEROS 2.5D 3D,和Foveros Direct 3D。 [Intel Advanced Package:帮助非常心爱的AI芯片的技术力量]左上方:FCBGA 2D,右上:2.5D,左下:Foveros 2.5D 3D,右下:EMIB 3.5D L FCBGA 2D是传统的有机FCBGA(FLIP CHIP BALL GRIDAY套件),适合产品和低I/O量。 L FCBGA 2D+已将基材技术添加到此基础上,这可以降低相互关联并降低成本,特别适用于网络和转移设备等产品。 L EMIB(嵌入式多芯片互连桥)2.5D技术通过微型硅桥连接芯片与基板,适用于高密度的芯片间连接,并在AI场外和高性能计算(HPC)之外进行。 IPIL EMIB 3.5D在此基础上识别3D估计技术。芯片可以在主动或被动基材上垂直垂直定位,然后通过EMIB技术连接,从而提高灵活性并允许您根据IP的特征选择垂直或水平搜索,同时避免使用大型介体。 l Foveros 2.5D和3D技术采用了基于焊接而不是基板连接的焊料,适用于高速I/O和较小的组分离芯片。 L Foveros Direct 3D技术通过直接铜和铜粘结提供了出色的性能。值得注意的是,这些技术并非既有独家店,而是可以在包装中同时采用的,从而为复杂芯片设计提供了极大的灵活性。 SA商业级别,它反映了英特尔对包装细分市场的强调。 EMIB:正确的AI芯片包装。从AI芯片的包装包装中,EMIV 2.5D技术与其他晶圆级2.5D行业技术相比,EMIV 2.5D技术具有许多优势,例如硅间插孔层和层的复活(RDL):[Intel Advanced Advanced Packaging:技术力量:有助于E的技术力量。Fifient AI技术集成了人工智能技术。与传统的大型插入式层相比,它可以在制造过程中更好地使用晶圆区域,减少空间和资源浪费,并且总成本较低。 l提高产量:EMIB技术已删除了晶圆级的组装步骤,从而降低了由模具和颠簸等复杂过程引起的损失产量的风险,从而可以改善一般制造过程的量化。 l工作效率:与晶圆级技术相比,EMIB技术的制造步骤较少,复杂性较低,因此其生产周期较短,可以节省宝贵的时间。在市场动态的快速变化的情况下,这次的优势将帮助客户更快地获得产品验证数据并加速产品启动。 l优化的尺寸:晶圆水平技术需要在基板上方添加插波层,而EMIB嵌入了硅BRIDGE到基板,这大大提高了基板面积的使用率。同时,基板的大小对应于集成电路面板格式,并且在单个软件包中使用EMIB ProvideMore芯片以容纳更多的工作负载。 L供应链和容量:英特尔具有成熟的供应链和足够的生产能力,以确保EMIB可以满足客户对高级包装解决方案的需求。高级包装L Intel Technology的未来开发产生120×120mm的超大包装。 [英特尔高级包装:帮助AI芯片的大型整合的技术力量]英特尔计划在未来几年内推出玻璃基板。玻璃基板可以承受更高的温度,将图案屈曲降低50%,并且具有非常低的平面性,改善光刻焦点的深度,并实现实现过度拥挤的中间层互连叠加所需的尺寸稳定性对于这些独特的特性,玻璃基板上的互连密度预计将增加10倍。另外,对于超大包装尺寸,机械玻璃性能的改进已经达到了很高的收率。此外,在较高温度下的玻璃基板的耐受性还提供了芯片建筑师,以设置电力传递和信号设计策略的灵活性,例如无缝将光学互连设备以及玻璃中的空气电感器和电容器相结合。因此,玻璃基板的采用可以实现更好的电力传输解决方案,同时以较低的电力消耗获得所需的高速信号,这有助于使整个行业更接近将1万亿晶体管纳入2030年的单个包装。

本文将帮助您了解高级英特尔技术流程和高级系统水平技术的全部细节...由本文引用:1。英特尔18A流媒体流媒体流式传输过程的技术过程将于2025年上半年完成。在2025年底启动。在2025年底启动,并将在2026年的上半年发布2026年的Inter forter for 2025 Intel forter Intel intel intel intel intel intel intel intel intel intel intel forter intel intel intel forty forty forter intel intel inter 3 efters forty forter intel int forty forter的范围的3季度与Intel 3的增长相比。预计芯片密度将增长15%,增加30%。 【英特尔18a |查看我们最大的变化过程】Intel 18a采用了两个主要的技术突破:彩色链接式晶体管技术和电源Backvia电源技术。 【英特尔18a |查看我们的MostribbonFet更改libbonFet完全浸没的栅极晶体管的过程:在芯片工艺技术的连续演变过程中,作为CHIP密度不断增加,泄漏问题引起的现象的变暖似乎是一种“诅咒”,并且已成为前路的主要障碍之一。色带是解决这一挑战的有效解决方案。通过十多年来,英特尔(Intel)是英特尔(Intel)最重要的晶体管技术之一,英特尔(Intel)实施了完全广泛的栅极体系结构(GAA),并具有垂直堆叠的色带通道,提高了晶体管的密度和能量效率,从而实现了准确的当前控制,并减少了进一步的问题,以实现进一步的跨跨晶体管收缩问题。此外,功能区FET在静电性能时改善了每个瓦的性能,最小电压(VMIN)操作。无论电压是什么,它都可以提供更强的电流驾驶,从而使晶体管开关更快,从而进一步改善了晶体管性能。色带还通过不同的带和多种类型的阈值(VT)电压提供了高度的可调性CH为芯片设计带来了更大的灵活性。 L Powervia背部电源:随着越来越多的使用情况需要较小,更高的密度和更强的性能晶体管才能满足计算强度不断增长的需求,而混合信号线和电源总是在晶圆中“抓住”相同的空间,从而导致晶体管紧密和增加晶体管。电力侧供应技术Powervia出现通过将粗金属层和颠簸在芯片后面移动,并将纳米尺度通过硅孔(Nano-TSV)嵌入到每个通用电池中,以提高电源的效率。这项技术在ISO4%功耗方面取得了最大的提高,大大降低了自然电阻(IR)以降低和提高单位使用5%至10%。 2024年2月,英特尔扩大了其路线图:[Process Node,Team Pele of] L Intel 14A使用高EUV技术,并有望在2027年之前实现大规模的大规模劳动。LIntel还计划推出更改的节点AL的版本ONG以满足客户不同需求的方式。其中,P版本至少获得了5%的性能提高(Intel 18A-P); E的折叠已扩大其功能,例如RF和电压调节(Intel 16-E,Intel 3-E,Intel 14a-E);通过使用Silicon(Intel 3-T,Intel 3-PT)使用孔,为3D堆叠进行了优化的T版本。 2。包装技术高级包装高级包装技术的重要性可以将单个设备上的各种功能,流程,大小和制造商的芯片结合在一起,并以灵活,有效的能源和经济成本的方式创建基于系统的(SOC)芯片。因此,更多的AI芯片制造商更喜欢这项技术。 [英特尔高级包装:有助于大型AI芯片集成的技术力量]英特尔英特尔的高级包装解决方案以及先进的系统包装和测试(Intel Foundry ASAT),包括FCBGA 2D,FCBGA 2D+,2.5D,2.5D,EMIB 3.5D,FOVEROS 2.5D 3D,和Foveros Direct 3D。 [Intel Advanced Package:帮助非常心爱的AI芯片的技术力量]左上方:FCBGA 2D,右上:2.5D,左下:Foveros 2.5D 3D,右下:EMIB 3.5D L FCBGA 2D是传统的有机FCBGA(FLIP CHIP BALL GRIDAY套件),适合产品和低I/O量。 L FCBGA 2D+已将基材技术添加到此基础上,这可以降低相互关联并降低成本,特别适用于网络和转移设备等产品。 L EMIB(嵌入式多芯片互连桥)2.5D技术通过微型硅桥连接芯片与基板,适用于高密度的芯片间连接,并在AI场外和高性能计算(HPC)之外进行。 IPIL EMIB 3.5D在此基础上识别3D估计技术。芯片可以在主动或被动基材上垂直垂直定位,然后通过EMIB技术连接,从而提高灵活性并允许您根据IP的特征选择垂直或水平搜索,同时避免使用大型介体。 l Foveros 2.5D和3D技术采用了基于焊接而不是基板连接的焊料,适用于高速I/O和较小的组分离芯片。 L Foveros Direct 3D技术通过直接铜和铜粘结提供了出色的性能。值得注意的是,这些技术并非既有独家店,而是可以在包装中同时采用的,从而为复杂芯片设计提供了极大的灵活性。 SA商业级别,它反映了英特尔对包装细分市场的强调。 EMIB:正确的AI芯片包装。从AI芯片的包装包装中,EMIV 2.5D技术与其他晶圆级2.5D行业技术相比,EMIV 2.5D技术具有许多优势,例如硅间插孔层和层的复活(RDL):[Intel Advanced Advanced Packaging:技术力量:有助于E的技术力量。Fifient AI技术集成了人工智能技术。与传统的大型插入式层相比,它可以在制造过程中更好地使用晶圆区域,减少空间和资源浪费,并且总成本较低。 l提高产量:EMIB技术已删除了晶圆级的组装步骤,从而降低了由模具和颠簸等复杂过程引起的损失产量的风险,从而可以改善一般制造过程的量化。 l工作效率:与晶圆级技术相比,EMIB技术的制造步骤较少,复杂性较低,因此其生产周期较短,可以节省宝贵的时间。在市场动态的快速变化的情况下,这次的优势将帮助客户更快地获得产品验证数据并加速产品启动。 l优化的尺寸:晶圆水平技术需要在基板上方添加插波层,而EMIB嵌入了硅BRIDGE到基板,这大大提高了基板面积的使用率。同时,基板的大小对应于集成电路面板格式,并且在单个软件包中使用EMIB ProvideMore芯片以容纳更多的工作负载。 L供应链和容量:英特尔具有成熟的供应链和足够的生产能力,以确保EMIB可以满足客户对高级包装解决方案的需求。高级包装L Intel Technology的未来开发产生120×120mm的超大包装。 [英特尔高级包装:帮助AI芯片的大型整合的技术力量]英特尔计划在未来几年内推出玻璃基板。玻璃基板可以承受更高的温度,将图案屈曲降低50%,并且具有非常低的平面性,改善光刻焦点的深度,并实现实现过度拥挤的中间层互连叠加所需的尺寸稳定性对于这些独特的特性,玻璃基板上的互连密度预计将增加10倍。另外,对于超大包装尺寸,机械玻璃性能的改进已经达到了很高的收率。此外,在较高温度下的玻璃基板的耐受性还提供了芯片建筑师,以设置电力传递和信号设计策略的灵活性,例如无缝将光学互连设备以及玻璃中的空气电感器和电容器相结合。因此,玻璃基板的采用可以实现更好的电力传输解决方案,同时以较低的电力消耗获得所需的高速信号,这有助于使整个行业更接近将1万亿晶体管纳入2030年的单个包装。

本文将帮助您了解高级英特尔技术流程和高级系统水平技术的全部细节...由本文引用:1。英特尔18A流媒体流媒体流式传输过程的技术过程将于2025年上半年完成。在2025年底启动。在2025年底启动,并将在2026年的上半年发布2026年的Inter forter for 2025 Intel forter Intel intel intel intel intel intel intel intel intel intel intel forter intel intel intel forty forty forter intel intel inter 3 efters forty forter intel int forty forter的范围的3季度与Intel 3的增长相比。预计芯片密度将增长15%,增加30%。 【英特尔18a |查看我们最大的变化过程】Intel 18a采用了两个主要的技术突破:彩色链接式晶体管技术和电源Backvia电源技术。 【英特尔18a |查看我们的MostribbonFet更改libbonFet完全浸没的栅极晶体管的过程:在芯片工艺技术的连续演变过程中,作为CHIP密度不断增加,泄漏问题引起的现象的变暖似乎是一种“诅咒”,并且已成为前路的主要障碍之一。色带是解决这一挑战的有效解决方案。通过十多年来,英特尔(Intel)是英特尔(Intel)最重要的晶体管技术之一,英特尔(Intel)实施了完全广泛的栅极体系结构(GAA),并具有垂直堆叠的色带通道,提高了晶体管的密度和能量效率,从而实现了准确的当前控制,并减少了进一步的问题,以实现进一步的跨跨晶体管收缩问题。此外,功能区FET在静电性能时改善了每个瓦的性能,最小电压(VMIN)操作。无论电压是什么,它都可以提供更强的电流驾驶,从而使晶体管开关更快,从而进一步改善了晶体管性能。色带还通过不同的带和多种类型的阈值(VT)电压提供了高度的可调性CH为芯片设计带来了更大的灵活性。 L Powervia背部电源:随着越来越多的使用情况需要较小,更高的密度和更强的性能晶体管才能满足计算强度不断增长的需求,而混合信号线和电源总是在晶圆中“抓住”相同的空间,从而导致晶体管紧密和增加晶体管。电力侧供应技术Powervia出现通过将粗金属层和颠簸在芯片后面移动,并将纳米尺度通过硅孔(Nano-TSV)嵌入到每个通用电池中,以提高电源的效率。这项技术在ISO4%功耗方面取得了最大的提高,大大降低了自然电阻(IR)以降低和提高单位使用5%至10%。 2024年2月,英特尔扩大了其路线图:[Process Node,Team Pele of] L Intel 14A使用高EUV技术,并有望在2027年之前实现大规模的大规模劳动。LIntel还计划推出更改的节点AL的版本ONG以满足客户不同需求的方式。其中,P版本至少获得了5%的性能提高(Intel 18A-P); E的折叠已扩大其功能,例如RF和电压调节(Intel 16-E,Intel 3-E,Intel 14a-E);通过使用Silicon(Intel 3-T,Intel 3-PT)使用孔,为3D堆叠进行了优化的T版本。 2。包装技术高级包装高级包装技术的重要性可以将单个设备上的各种功能,流程,大小和制造商的芯片结合在一起,并以灵活,有效的能源和经济成本的方式创建基于系统的(SOC)芯片。因此,更多的AI芯片制造商更喜欢这项技术。 [英特尔高级包装:有助于大型AI芯片集成的技术力量]英特尔英特尔的高级包装解决方案以及先进的系统包装和测试(Intel Foundry ASAT),包括FCBGA 2D,FCBGA 2D+,2.5D,2.5D,EMIB 3.5D,FOVEROS 2.5D 3D,和Foveros Direct 3D。 [Intel Advanced Package:帮助非常心爱的AI芯片的技术力量]左上方:FCBGA 2D,右上:2.5D,左下:Foveros 2.5D 3D,右下:EMIB 3.5D L FCBGA 2D是传统的有机FCBGA(FLIP CHIP BALL GRIDAY套件),适合产品和低I/O量。 L FCBGA 2D+已将基材技术添加到此基础上,这可以降低相互关联并降低成本,特别适用于网络和转移设备等产品。 L EMIB(嵌入式多芯片互连桥)2.5D技术通过微型硅桥连接芯片与基板,适用于高密度的芯片间连接,并在AI场外和高性能计算(HPC)之外进行。 IPIL EMIB 3.5D在此基础上识别3D估计技术。芯片可以在主动或被动基材上垂直垂直定位,然后通过EMIB技术连接,从而提高灵活性并允许您根据IP的特征选择垂直或水平搜索,同时避免使用大型介体。 l Foveros 2.5D和3D技术采用了基于焊接而不是基板连接的焊料,适用于高速I/O和较小的组分离芯片。 L Foveros Direct 3D技术通过直接铜和铜粘结提供了出色的性能。值得注意的是,这些技术并非既有独家店,而是可以在包装中同时采用的,从而为复杂芯片设计提供了极大的灵活性。 SA商业级别,它反映了英特尔对包装细分市场的强调。 EMIB:正确的AI芯片包装。从AI芯片的包装包装中,EMIV 2.5D技术与其他晶圆级2.5D行业技术相比,EMIV 2.5D技术具有许多优势,例如硅间插孔层和层的复活(RDL):[Intel Advanced Advanced Packaging:技术力量:有助于E的技术力量。Fifient AI技术集成了人工智能技术。与传统的大型插入式层相比,它可以在制造过程中更好地使用晶圆区域,减少空间和资源浪费,并且总成本较低。 l提高产量:EMIB技术已删除了晶圆级的组装步骤,从而降低了由模具和颠簸等复杂过程引起的损失产量的风险,从而可以改善一般制造过程的量化。 l工作效率:与晶圆级技术相比,EMIB技术的制造步骤较少,复杂性较低,因此其生产周期较短,可以节省宝贵的时间。在市场动态的快速变化的情况下,这次的优势将帮助客户更快地获得产品验证数据并加速产品启动。 l优化的尺寸:晶圆水平技术需要在基板上方添加插波层,而EMIB嵌入了硅BRIDGE到基板,这大大提高了基板面积的使用率。同时,基板的大小对应于集成电路面板格式,并且在单个软件包中使用EMIB ProvideMore芯片以容纳更多的工作负载。 L供应链和容量:英特尔具有成熟的供应链和足够的生产能力,以确保EMIB可以满足客户对高级包装解决方案的需求。高级包装L Intel Technology的未来开发产生120×120mm的超大包装。 [英特尔高级包装:帮助AI芯片的大型整合的技术力量]英特尔计划在未来几年内推出玻璃基板。玻璃基板可以承受更高的温度,将图案屈曲降低50%,并且具有非常低的平面性,改善光刻焦点的深度,并实现实现过度拥挤的中间层互连叠加所需的尺寸稳定性对于这些独特的特性,玻璃基板上的互连密度预计将增加10倍。另外,对于超大包装尺寸,机械玻璃性能的改进已经达到了很高的收率。此外,在较高温度下的玻璃基板的耐受性还提供了芯片建筑师,以设置电力传递和信号设计策略的灵活性,例如无缝将光学互连设备以及玻璃中的空气电感器和电容器相结合。因此,玻璃基板的采用可以实现更好的电力传输解决方案,同时以较低的电力消耗获得所需的高速信号,这有助于使整个行业更接近将1万亿晶体管纳入2030年的单个包装。

本文将帮助您了解高级英特尔技术流程和高级系统水平技术的全部细节...由本文引用:1。英特尔18A流媒体流媒体流式传输过程的技术过程将于2025年上半年完成。在2025年底启动。在2025年底启动,并将在2026年的上半年发布2026年的Inter forter for 2025 Intel forter Intel intel intel intel intel intel intel intel intel intel intel forter intel intel intel forty forty forter intel intel inter 3 efters forty forter intel int forty forter的范围的3季度与Intel 3的增长相比。预计芯片密度将增长15%,增加30%。 【英特尔18a |查看我们最大的变化过程】Intel 18a采用了两个主要的技术突破:彩色链接式晶体管技术和电源Backvia电源技术。 【英特尔18a |查看我们的MostribbonFet更改libbonFet完全浸没的栅极晶体管的过程:在芯片工艺技术的连续演变过程中,作为CHIP密度不断增加,泄漏问题引起的现象的变暖似乎是一种“诅咒”,并且已成为前路的主要障碍之一。色带是解决这一挑战的有效解决方案。通过十多年来,英特尔(Intel)是英特尔(Intel)最重要的晶体管技术之一,英特尔(Intel)实施了完全广泛的栅极体系结构(GAA),并具有垂直堆叠的色带通道,提高了晶体管的密度和能量效率,从而实现了准确的当前控制,并减少了进一步的问题,以实现进一步的跨跨晶体管收缩问题。此外,功能区FET在静电性能时改善了每个瓦的性能,最小电压(VMIN)操作。无论电压是什么,它都可以提供更强的电流驾驶,从而使晶体管开关更快,从而进一步改善了晶体管性能。色带还通过不同的带和多种类型的阈值(VT)电压提供了高度的可调性CH为芯片设计带来了更大的灵活性。 L Powervia背部电源:随着越来越多的使用情况需要较小,更高的密度和更强的性能晶体管才能满足计算强度不断增长的需求,而混合信号线和电源总是在晶圆中“抓住”相同的空间,从而导致晶体管紧密和增加晶体管。电力侧供应技术Powervia出现通过将粗金属层和颠簸在芯片后面移动,并将纳米尺度通过硅孔(Nano-TSV)嵌入到每个通用电池中,以提高电源的效率。这项技术在ISO4%功耗方面取得了最大的提高,大大降低了自然电阻(IR)以降低和提高单位使用5%至10%。 2024年2月,英特尔扩大了其路线图:[Process Node,Team Pele of] L Intel 14A使用高EUV技术,并有望在2027年之前实现大规模的大规模劳动。LIntel还计划推出更改的节点AL的版本ONG以满足客户不同需求的方式。其中,P版本至少获得了5%的性能提高(Intel 18A-P); E的折叠已扩大其功能,例如RF和电压调节(Intel 16-E,Intel 3-E,Intel 14a-E);通过使用Silicon(Intel 3-T,Intel 3-PT)使用孔,为3D堆叠进行了优化的T版本。 2。包装技术高级包装高级包装技术的重要性可以将单个设备上的各种功能,流程,大小和制造商的芯片结合在一起,并以灵活,有效的能源和经济成本的方式创建基于系统的(SOC)芯片。因此,更多的AI芯片制造商更喜欢这项技术。 [英特尔高级包装:有助于大型AI芯片集成的技术力量]英特尔英特尔的高级包装解决方案以及先进的系统包装和测试(Intel Foundry ASAT),包括FCBGA 2D,FCBGA 2D+,2.5D,2.5D,EMIB 3.5D,FOVEROS 2.5D 3D,和Foveros Direct 3D。 [Intel Advanced Package:帮助非常心爱的AI芯片的技术力量]左上方:FCBGA 2D,右上:2.5D,左下:Foveros 2.5D 3D,右下:EMIB 3.5D L FCBGA 2D是传统的有机FCBGA(FLIP CHIP BALL GRIDAY套件),适合产品和低I/O量。 L FCBGA 2D+已将基材技术添加到此基础上,这可以降低相互关联并降低成本,特别适用于网络和转移设备等产品。 L EMIB(嵌入式多芯片互连桥)2.5D技术通过微型硅桥连接芯片与基板,适用于高密度的芯片间连接,并在AI场外和高性能计算(HPC)之外进行。 IPIL EMIB 3.5D在此基础上识别3D估计技术。芯片可以在主动或被动基材上垂直垂直定位,然后通过EMIB技术连接,从而提高灵活性并允许您根据IP的特征选择垂直或水平搜索,同时避免使用大型介体。 l Foveros 2.5D和3D技术采用了基于焊接而不是基板连接的焊料,适用于高速I/O和较小的组分离芯片。 L Foveros Direct 3D技术通过直接铜和铜粘结提供了出色的性能。值得注意的是,这些技术并非既有独家店,而是可以在包装中同时采用的,从而为复杂芯片设计提供了极大的灵活性。 SA商业级别,它反映了英特尔对包装细分市场的强调。 EMIB:正确的AI芯片包装。从AI芯片的包装包装中,EMIV 2.5D技术与其他晶圆级2.5D行业技术相比,EMIV 2.5D技术具有许多优势,例如硅间插孔层和层的复活(RDL):[Intel Advanced Advanced Packaging:技术力量:有助于E的技术力量。Fifient AI技术集成了人工智能技术。与传统的大型插入式层相比,它可以在制造过程中更好地使用晶圆区域,减少空间和资源浪费,并且总成本较低。 l提高产量:EMIB技术已删除了晶圆级的组装步骤,从而降低了由模具和颠簸等复杂过程引起的损失产量的风险,从而可以改善一般制造过程的量化。 l工作效率:与晶圆级技术相比,EMIB技术的制造步骤较少,复杂性较低,因此其生产周期较短,可以节省宝贵的时间。在市场动态的快速变化的情况下,这次的优势将帮助客户更快地获得产品验证数据并加速产品启动。 l优化的尺寸:晶圆水平技术需要在基板上方添加插波层,而EMIB嵌入了硅BRIDGE到基板,这大大提高了基板面积的使用率。同时,基板的大小对应于集成电路面板格式,并且在单个软件包中使用EMIB ProvideMore芯片以容纳更多的工作负载。 L供应链和容量:英特尔具有成熟的供应链和足够的生产能力,以确保EMIB可以满足客户对高级包装解决方案的需求。高级包装L Intel Technology的未来开发产生120×120mm的超大包装。 [英特尔高级包装:帮助AI芯片的大型整合的技术力量]英特尔计划在未来几年内推出玻璃基板。玻璃基板可以承受更高的温度,将图案屈曲降低50%,并且具有非常低的平面性,改善光刻焦点的深度,并实现实现过度拥挤的中间层互连叠加所需的尺寸稳定性对于这些独特的特性,玻璃基板上的互连密度预计将增加10倍。另外,对于超大包装尺寸,机械玻璃性能的改进已经达到了很高的收率。此外,在较高温度下的玻璃基板的耐受性还提供了芯片建筑师,以设置电力传递和信号设计策略的灵活性,例如无缝将光学互连设备以及玻璃中的空气电感器和电容器相结合。因此,玻璃基板的采用可以实现更好的电力传输解决方案,同时以较低的电力消耗获得所需的高速信号,这有助于使整个行业更接近将1万亿晶体管纳入2030年的单个包装。